1. 前言

在之前已经完成了data域与signal域的数据的处理,在构建整个802.11a OFDM数据帧的时候,只剩下前导码这部分的内容还没有实现了。

2. 前导码

2.1 短训练序列

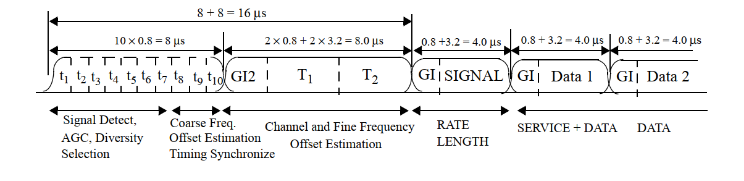

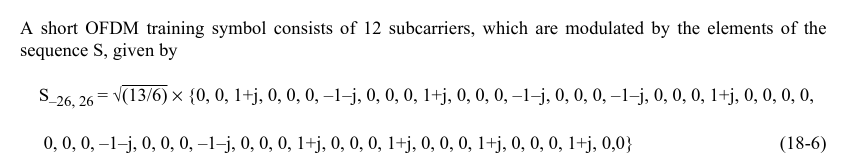

短训练序列的主要用途是进行信号的检测、AGC和粗频偏估计。短训练序列都是经过精心的设计,每个短训练序列的长度为0.8us,在802.11a的前导码当中一共有10个短训练序列。这些短训练序列符号占据每个OFDM符号的52个非零子载波当中的12个。如果用-26~26来标识非零子载波的话,那么短训练序列的子载波的序号为{-24, -20, -16, -12, -8, -4, 4, 8, 12, 16, 20, 24},其中传输的传输数据为一个固定的伪随机序列,采用的QPSK的映射方式。

由于短训练序列只用了52个子载波当中12个来传输符号,因此为了保证OFDM符号的功率稳定,需要乘以因子 $\sqrt{13/6}$.

短训练序列的的选择可以是的在较大的范围内实现粗频率估计,通常对于周期为T的重复符号而言,最大可估计的频率偏差为1/2T,因此通过测量连续两个长度为0.8us的短训练序列符号的相位差,可以估计的频率偏差可达625KHz。

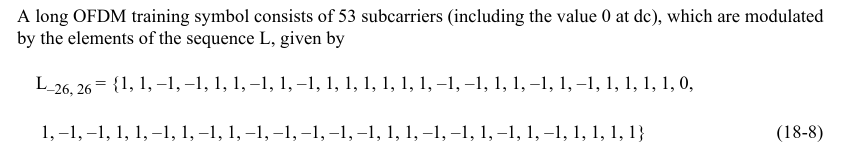

2.2 长训练序列

长训练序列的紧跟在短训练序列之后,长度为8us,长训练序列符号与正常的OFDM符号一样由53个子载波(包含直流处的空子载波)组成,分别占据-26~26信道,长训练序列采用传输的是BPSK符号。表示为:

在实际使用过程当中,由与短训练序列和长训练序列是固定的,因此可以先使用matlab,python等工具先将短训练序列和长训练序列生成出来,然后将序列存储在ROM当中,在使用的时候,直接从ROM当中读取出来就可以了。

3.训练序列生成

由于训练序列是一个固定的序列,因此,我们可以先使用matlab等工具来实现生成这些序列,并将这些荀烈存储在RAM当中,这样在之后,只需要从RAM中将训练序列读取出来即可。

从前面的介绍可以知道,一共有10个短训练序列和2个长训练序列。实现这部分的matlab代码如下:

1 | clear all; |

在上面的代码当中,将训练序列按照10个长训练序列,一个长训练序列保护间隔,2个长训练序列的方式进行排列,这样就可以最终生成实部和虚部的coe文件,通过这个coe文件就能够在FPGA当中获得输出的前导码的信号。

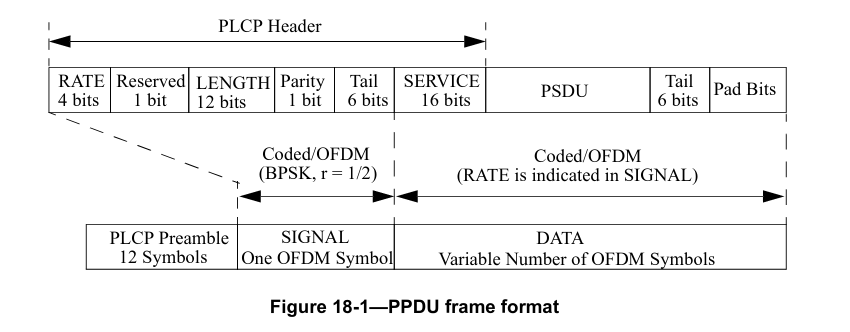

4. 构建完整PLCP帧

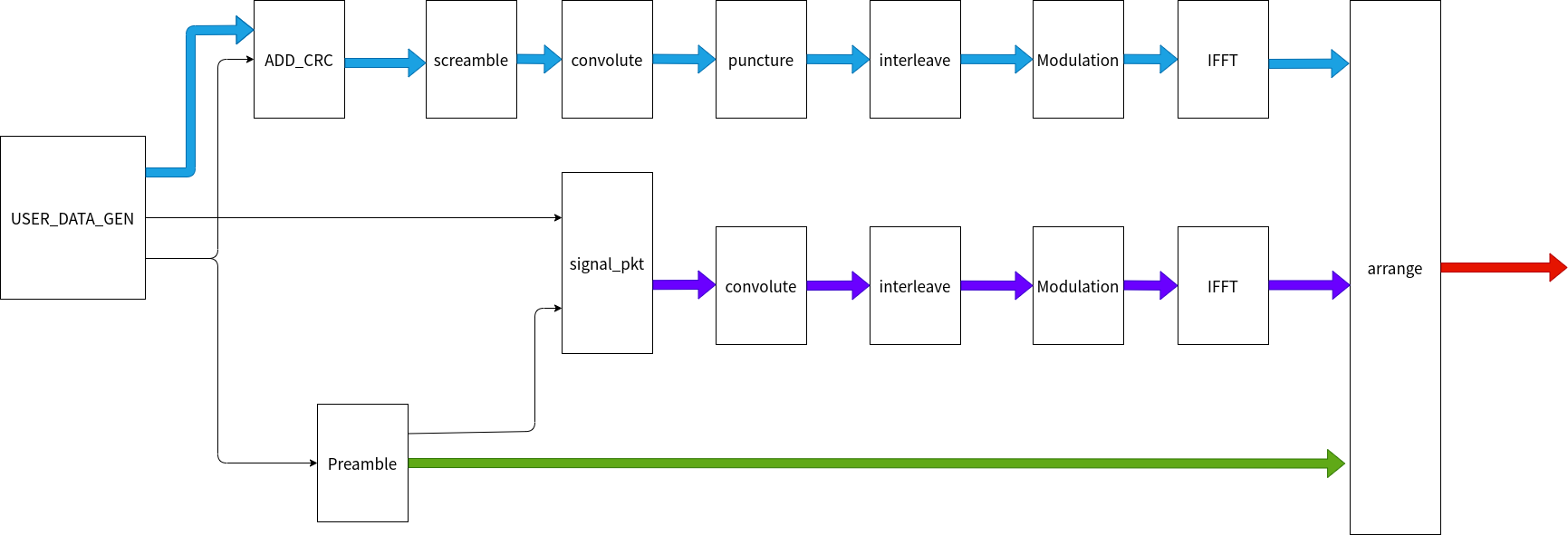

在了解了前导码如何生成之后,就可以将前导码,signal域,data域的数据全部组合在一起实现一个完整的plcp数据帧了。最终将这个plcp信号帧通过AD9361发送出去就完成了ofdm的发送部分。

实现的思路是:按照前导码,signal域,data域的数据进行排列,将这些数据全部缓存到一个FIFO当中,当所有的数据都写入到FIFO之后,再从FIFO中将这一帧数据读出取来,从而实现一个完整的数据帧。

为了能够兼容更大带宽的设计,采样率可以支持40M和20M,当采样率为40M的时候,直接将前面实现的那些模块生成的数据缓存到FIFO当中即可,但是如果使用20M采样率的时候,需要将前面实现的模块生成的数据进行一个1/2的抽取,才能作为最终的信号输出。

实现的时序如下图所示:

具体的实现代码如下:

1 |

|