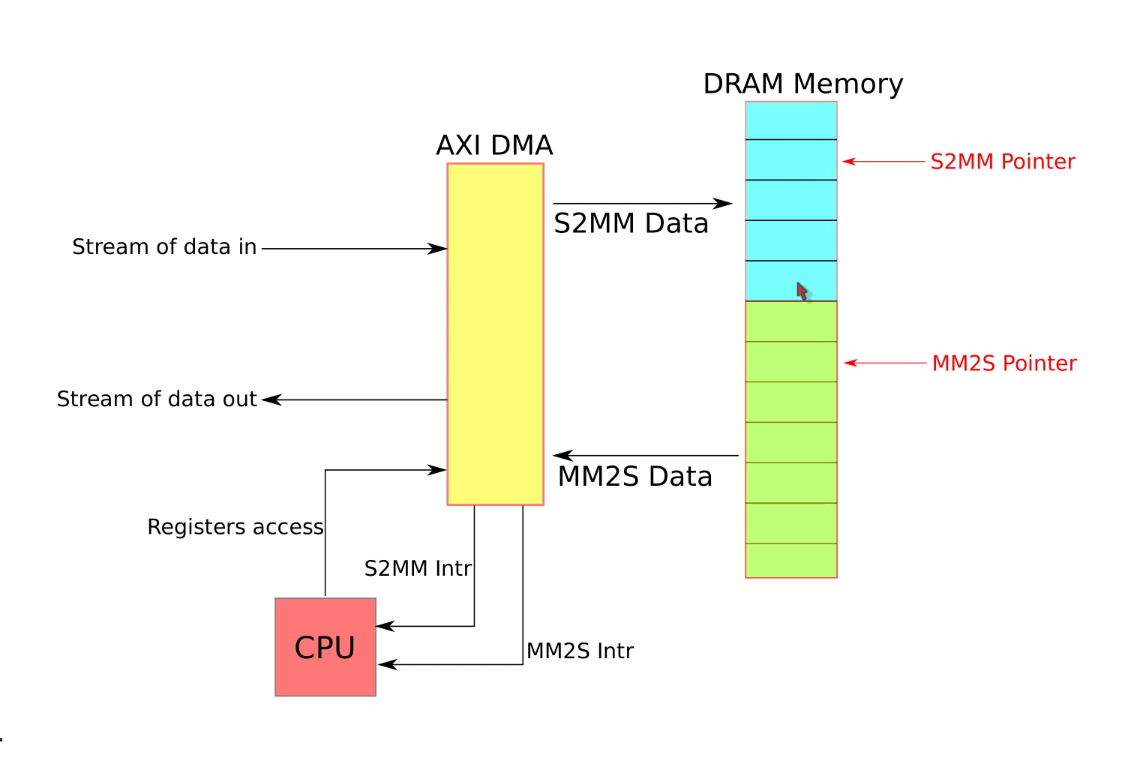

1. 基本结构

AXI DMA工作的基本结果如下,AXI DMA负责和内存进行数据交互,一条路径是S2MM也就是将PL侧产生的用户数据写入到内存当中,另外一条路径是MM2S也就是将用户数据从内存当中读取出来给到用户逻辑。

最近挺迷茫的,但是今天稍微深入地了解了一个之前见过的公司,也就是提供ZipCPU的这个公司,这个IP,在ettus usrp的之前的系列当中用过,是一个比较完整的处理器。

这是由一个人完成的公司,在了解了这个公司之后,我发现了他开源了许多和FPGA相关的资源,包括这个ZipCPU,DSP处理相关的资源等等。

看到了他实现的这一些列工作之后,我一时间感觉到了相当震惊。

因为现在在ubuntu下工作的时间比较多,一直在找一个在ubuntu上比较好用的仿真软件,vivado自带的仿真工具感觉不太好用。

经过一番搜索之后,也算是找到一个还算好用的仿真软件,当然我是用的破解版本。所以准备记录一下安装过程。这篇博客的用途仅仅是为了我自己日后方便查阅。

主要参考下面的博主的博客:

questasim安装